Technical Guide 2024

CeraLink Capacitors

www.tdk-electronics.tdk.com

| Table of contents                                                                                                                                             |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| General remark                                                                                                                                                | 3        |

| Capacitance                                                                                                                                                   | 3        |

| • Measurement of $C_0$ (initial capacitance) and $C_{eff}$ (effective capacitance)                                                                            | 6        |

| Measurement of C <sub>nom</sub> (nominal capacitance)                                                                                                         | 6        |

| Temperature dependence of capacitance                                                                                                                         | 8        |

| <ul> <li>Frequency dependence of capacitance</li> </ul>                                                                                                       | 12       |

| Capacitance calculation                                                                                                                                       | 13       |

| Current capability                                                                                                                                            | 14       |

| Polarization                                                                                                                                                  | 16       |

| Voltage                                                                                                                                                       | 16       |

| De-polarization over time                                                                                                                                     | 17       |

| De-polarization over temperature                                                                                                                              | 17       |

| Overview                                                                                                                                                      | 18       |

| CeraLink lifetime model & lifetime estimation                                                                                                                 | 19       |

| <ul> <li>Characteristic lifetime, reliability and failure distribution</li> </ul>                                                                             | 19       |

| Systems of identical chips                                                                                                                                    | 20       |

| <ul> <li>Mission profiles and combined failure distributions</li> </ul>                                                                                       | 21       |

| Calculation example I – constant operating conditions                                                                                                         | 22       |

| Calculation example II – simplified mission profile                                                                                                           | 23       |

| Frequently asked questions                                                                                                                                    | 24       |

| <ul> <li>How do I detect if CeraLink is poled or unpoled?</li> </ul>                                                                                          | 24       |

| • CeraLink seems to be partly poled/unpoled (e.g. after reflow soldering). How shall I proceed?                                                               | 24       |

| <ul> <li>If CeraLink is poled, how do I detect the poling direction?</li> </ul>                                                                               | 24       |

| What happens if a CeraLink capacitor is mounted in the wrong polarity direction?                                                                              | 24       |

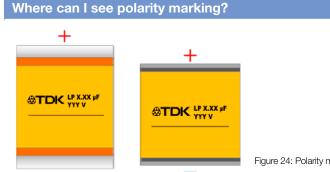

| • Where can I see polarity marking?                                                                                                                           | 24       |

| • You mention there is no limitation on dV/dT. How is this to be understood in regard to voltage                                                              | 05       |

| or current peaks in the milliseconds range?                                                                                                                   | 25<br>25 |

| <ul><li>What do I have to consider in regard to conformal coating?</li><li>What do I have to consider in regard to creepage and clearance distance?</li></ul> | 25<br>25 |

| Which soldering processes are applicable for CeraLink?                                                                                                        | 26       |

| How can I repair/rework soldering on CeraLink?                                                                                                                | 26       |

| Is CeraLink using the classical MLCC design?                                                                                                                  | 26       |

| Why can CeraLink handle so much current?                                                                                                                      | 27       |

| Pulse current and inrush current?                                                                                                                             | 27       |

| How much lead (Pb) contains CeraLink?                                                                                                                         | 27       |

| Which MSL does apply?                                                                                                                                         | 28       |

| Are balancing resistors needed when connecting CeraLink in series?                                                                                            | 28       |

| Appendices                                                                                                                                                    | 29       |

| • Glossary                                                                                                                                                    | 29       |

| CeraLink data sheet                                                                                                                                           | 30       |

| Design support                                                                                                                                                | 30       |

| Contact information                                                                                                                                           | 30       |

| Revision history                                                                                                                                              | 30       |

## **General remark**

This document is a guideline for engineers working with CeraLink. CeraLink is a PLZT (lead lanthanum zirconium titanate) based ceramic capacitor with anti-ferroelectric behavior, which is optimized for high frequency & high temperature power electronic applications. We exemplify this using figures and values of CeraLink LP 500 V series (P/N B58031I/U5105M 62) unless otherwise mentioned. Electrical characterization values for this type are:

| V <sub>pk, max</sub> | V <sub>R</sub> | V <sub>op</sub> | C <sub>nom, typ</sub> | C <sub>eff, typ</sub> | Co           |

|----------------------|----------------|-----------------|-----------------------|-----------------------|--------------|

| 650 V                | 500 V          | 400 V           | 1 µF                  | 0.6 µF                | 0.35 µF ±20% |

Table 1: Technical parameter for CeraLink LP 500 V

### The main features of CeraLink are:

- Increasing capacitance with DC bias between 0 V and  $V_{op}$  and best in class capacitance density at operating point ( $V_{op} \& T_{op}$ )

- High current capability due to low losses at high frequencies (up to several MHz) and high temperatures (up to +150 °C)

- Designed for high dV/dt ratios, i.e. suitable for fast switching, respectively, high switching frequencies (e.g. SiC or GaN applications)

- Good thermal self-regulating properties

- Qualification based on AEC-Q200

- RoHS-compatible PLZT ceramic (see RoHS exemption 7c-II). For detailed information please refer to the <u>TDK Environmental protection website</u>.

CeraLink is not recommended for operation under constant polarity change (AC voltage) due to increased self-heating induced by re-poling loses – please see chapter <u>>Polarization</u> for details.

### Capacitance

CeraLink features a non-linear capacitance behavior, i.e. the capacitance strongly depends on external parameters such as the applied DC bias voltage or the temperature. It is important to note that CeraLink is designed to have its capacitance maximum under operating conditions, where we distinguish two scenarios:

- 1. DC-Link operation, i.e. operation under a DC bias (constant operating voltage) and with a superimposed ripple amplitude. As explained in the following, for this scenario it depends on the amplitude of the superimposed ripple voltage, whether the effective capacitance  $C_{eff}$  or the nominal capacitance  $C_{nom}$  should be considered.\*

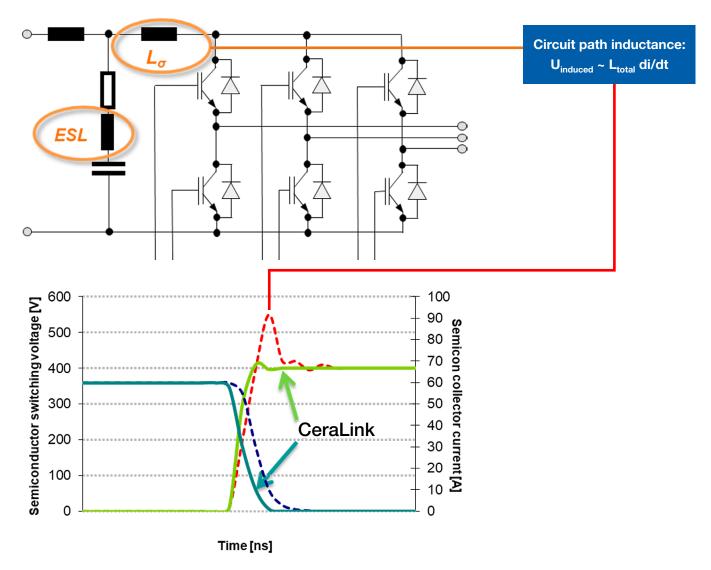

- 2. Snubbering/filtering, i.e. operation to filter out voltage spikes. These voltage spikes can be superimposed on a specific DC bias voltage, for example the characteristic voltage spikes that are superimposed on the operating voltage during fast semiconductor switching as shown in Figure 1, or the voltage spikes are induced by fast current switching of an inductive load, e.g. when disconnecting an electric motor or pump from the battery supply in a protection circuit. In this case, the voltage may start from 0 V to some peak voltage.

In all these scenarios, the applied current is limited only indirectly by the maximally rated device temperature of 150 °C, where we note that operation above rated temperature is possible in principle but not recommended since it will affect lifetime of the capacitor.

<sup>\*</sup> We note that the full nominal capacitance  $C_{nom}$  can be achieved only if the voltage seen by the CeraLink capacitor spans a sufficiently large range in the hysteresis loop as explained in section >Measurement of  $C_{nom}$  (nominal capacitance)<. This is typically fulfilled in a snubber application, where for DC link applications, it is usually not the case such that in this case a capacitance in a range between  $C_{eff}$  and  $C_{nom}$  can be obtained realistically. The exact value depends on the superimposed ripple amplitude. Further details will be provided in section >Capacitance Calculation<.

## Capacitance

Furthermore, the induced voltage spikes must not exceed the maximally allowed peak voltage  $V_{pk,max}$  for a given CeraLink type, i.e. short voltage pulses ranging from 0 V to  $V_{pk,max}$  are tolerable and there is no limit on dV/dt, respectively, dV/dt is limited by the intrinsic ESR of the capacitor.

Usually in all these scenarios, values close to the nominal capacitance  $C_{nom}$  can be considered. This is also commonly referred to as the large signal capacity. Details about the definition and how to measure the large signal capacitance are explained in section <u>>Measurement of</u>  $C_{nom}$  (nominal capacitance)<.

Figure 1: Semiconductor overshoot principle. The larger the overall inductance, the larger are the induced voltage spikes during switching. Thanks to the high temperature rating of 150 °C, CeraLink capacitors can be mounted close to the semiconductors and therefore minimizing the overall conductance loop.

### Capacitance

Note that the specific operating voltage  $V_{\rm op}$  for all CeraLink types is usually 100 V below the rated voltage  $V_{\rm R}$ , i.e. in case of the LP 500 V, the operating voltage is 400 V. This is also the regime in which the device provides the maximal capacitance.

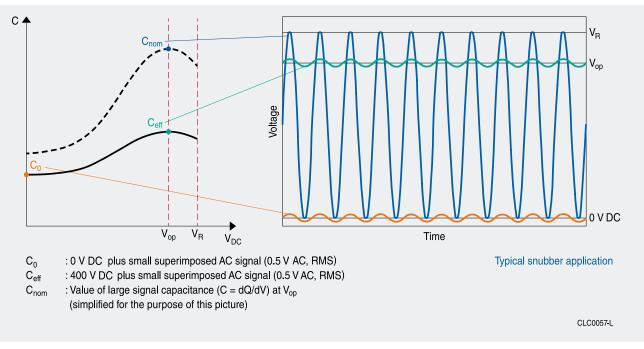

Due to this intrinsic non-linearity, there are usually three different capacitance values stated in the CeraLink data sheets: the initial capacitance  $C_0$ , the effective capacitance  $C_{eff}$ , and the nominal capacitance  $C_{nom}$ , where the latter value defines the rated capacitance of a CeraLink capacitor:

Initial capacitance Co: measured at 0 V DC, 0.5 V AC, RMS, 1 kHz, room temperature

This means no DC bias and just a small AC voltage is applied (this measurement corresponds to a usual incoming inspection test with LCR-meter)

Effective capacitance C<sub>eff</sub>: measured at operating voltage V<sub>op</sub>, 0.5 V AC, RMS, 1 kHz, room temperature

Same as the  $C_0$  measurement but with a DC bias (constant operating voltage), which is in this case operating voltage  $V_{op}$ . This measurement corresponds to the usual operation under DC link voltage with a small superimposed ripple amplitude. Throughout, this will be also denoted as the small signal capacitance.

Nominal capacitance  $C_{nom}$ : measured at operating voltage  $V_{op}$ , quasistatic, room temperature

The nominal capacitance value is derived from the maximum of the mean hysteresis through the common definition C = dQ/dV. Throughout, this will be also denoted as the large signal capacitance. The measurement is explained in the chapter <u>>Measurement of C<sub>nom</sub> (nominal capacitance)</u><.

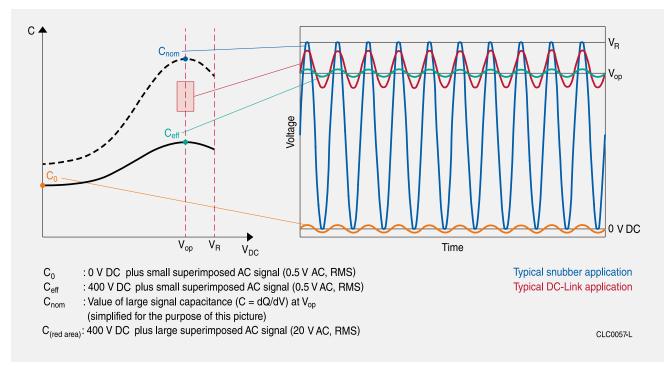

These definitions, together with the corresponding voltage scenarios are schematically depicted in Figure 2.

Figure 2: (left) Schematical representation of capacitance versus DC bias for small signal (solid line) and large signal (dashed line) and definition of the capacitance values  $C_0$ ,  $C_{eff}$  and  $C_{nom}$ . Note that the maxima of  $C_{eff}$  and  $C_{nom}$  not necessarily overlap, resp., can be slightly shifted around  $V_{ap}$ . (right) Schematical representation of corresponding voltage levels. The definition of small and large signal depends on the applied voltage signal. Here, for small superimposed ripple amplitudes (small signal), the effective capacitance  $C_{eff}$  should be considered, where in the limit of very large voltage amplitudes (large signal), the nominal capacitance  $C_{nom}$  can be considered.

## Capacitance

Measurement of C<sub>0</sub> (initial capacitance) and C<sub>eff</sub> (effective capacitance)

The initial capacitance  $C_0$  of CeraLink is defined using the following conditions: only a negligible external field is applied. That means that  $C_0$  is measured at zero DC bias voltage and with a small sinusoidal AC field of 0.5 V AC, RMS at 1 kHz oscillator frequency at room temperature (small signal). On the other hand, the effective capacitance  $C_{eff}$  is defined under the same conditions, but with a defined DC-bias applied. This means that  $C_{eff}$  is measured at operating voltage  $V_{op}$  with a small sinusoidal external field of 0.5 V AC, RMS at 1 kHz oscillator frequency at room temperature (small signal).

### Measurement of C<sub>nom</sub> (nominal capacitance)

The base is a quasi-static unipolar polarization measurement, where the electrical charge on the capacitor is monitored versus the voltage. The capacitance is then obtained from the derivative

$$C(V) = \frac{dQ}{dV}$$

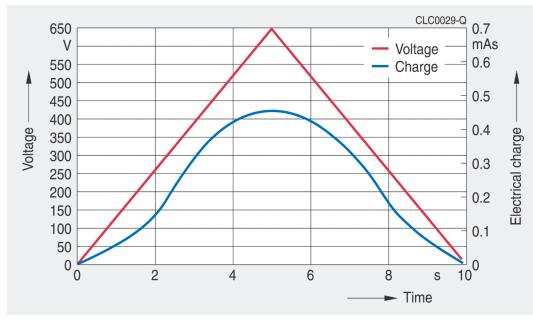

The term "quasi-static" means that the voltage level is increased slowly enough such that the charging current is not exceeding the maximum current limit of the measurement device. Since this depends on the used measurement equipment, it can vary. Here a dV/dt value of 100 to 500 V/s is a reasonable choice and will not influence the result, if the current can be handled by the equipment. For the measurement, the voltage is ramped up / down according to:

$V(t) = k \cdot t$

The triangular function should be chosen such that  $k = 100 \dots 500$  and the maximally applied voltage is slightly below or equal to  $V_{pk,max}$  for a given CeraLink type as defined in the data sheet.

The described measurement procedure and the polarization curve Q(V) is shown in the following diagrams:

Figure 3: Electrical charge and voltage versus measurement time.

Capacitance

Measurement of C<sub>nom</sub> (nominal capacitance)

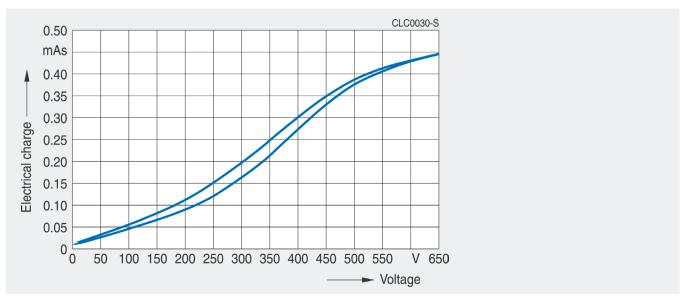

Figure 4: Electrical charge versus voltage. Note that the electrical charge will be different for different CeraLink types (in this case it is for a CeraLink LP 500 V capacitor).

The differential capacitance is defined via the derivative of the electrical charge with respect to the voltage, i.e. Applying the derivative to the polarization curve shown above results in the following diagram:

$$C(V) = \frac{dQ}{dV}$$

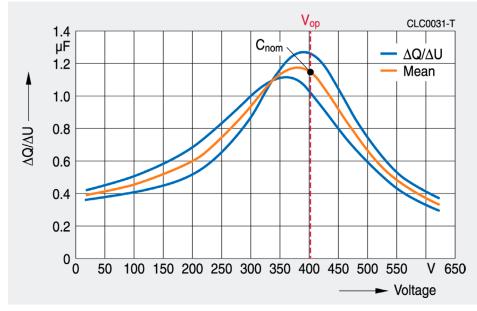

Figure 5: Derivative of hysteresis shown in Figure 4. C<sub>nom</sub> corresponds to the value of the mean curve at V<sub>op</sub>.

In a final step, the average between the two blue envelope curves is taken. Here, the value of the curve at operating voltage  $V_{op}$  corresponds to the nominal capacitance  $C_{nom}$  as defined in the data sheet.

This value corresponds roughly to the maximum of the curve, or phrased differently, the capacitance maximum of a CeraLink is centered around its respective operating voltage  $V_{on}$ .

Capacitance

Measurement of C<sub>nom</sub> (nominal capacitance)

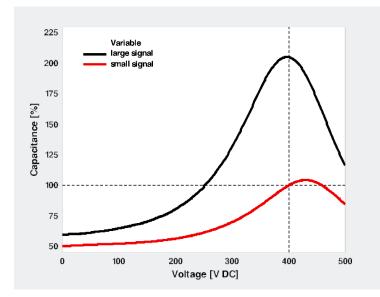

In Figure 6, the difference between the small signal capacitance and the large signal capacitance at room

temperature for a CeraLink is shown.

The 100% value corresponds to  $C_{\text{eff, typ}}$  as defined in the data sheet (see <u>Table 1</u> in this document for an example).

Small signal capacitance (red curve). The effective capacitance C<sub>eff</sub> corresponds to the value at

$V_{op} = 400 \text{ V DC}$

Large signal capacitance (black curve). The nominal capacitance C<sub>nom</sub> corresponds to the value at

$V_{00} = 400 \text{ V DC}$

Figure 6: Capacitance measurement at large and small signal for CeraLink LP 500 V. Note that the exact location of the capacitance maxima also depends on the device temperature as discussed in the next section.

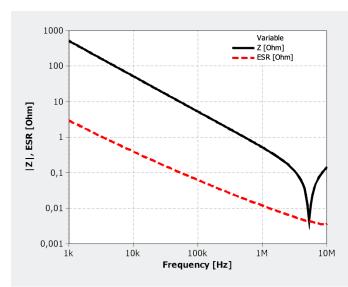

#### Temperature dependence of capacitance

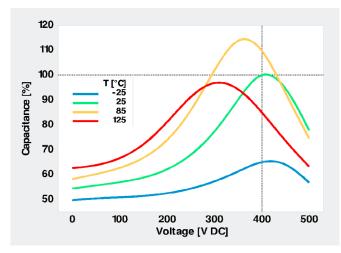

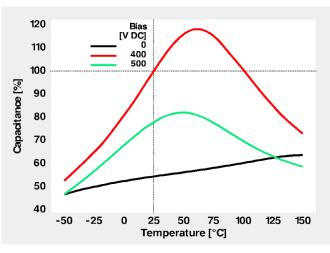

Capacitance of CeraLink depends on voltage (DC bias), superimposed ripple amplitude, frequency and ambient temperature applied. Whereas the dependence on frequency is usually small (see section <u>>Frequency</u> <u>Dependence of Capacitance<</u>), the dependence on temperature is sizeable as shown in the following figures and should be considered in application. Note that these non-linear properties of CeraLink are implemented in our simulation tool which is available via our website: <u>www.tdk-electronics.tdk.com</u>. This simulation tool comprises various LTSpice model libraries for most CeraLink types. It is intended to help engineers to easier design-in a specific CeraLink component in their application.

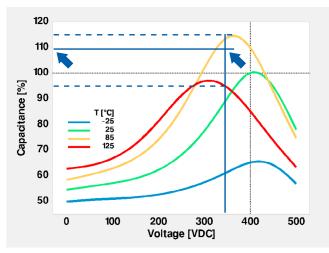

Figure 7: Voltage dependence of capacitance for different temperatures.\*

Figure 8: Temperature dependence of capacitance for different DC bias voltages.\*

\* The 100% value corresponds to C<sub>eff, typ</sub> as defined in the data sheet (see Table 1 in this document for an example).

## Capacitance

### Temperature dependence of capacitance

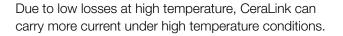

At operating voltage, the maximum in capacitance is reached at around 60 °C, so the optimal temperature for CeraLink is in the range of +50 to +90 °C at  $V_{op}$ . It is important to note that for lower temperatures, especially below 25 °C, the device will potentially heat up more quickly as compared to other ceramic capacitors (e.g. COG or X7R) to reach an optimal working point. This "feel-good" temperature can be significantly higher than the ambient temperature and is caused by the increased ESR at low temperatures as shown in Figure 10.

On the other hand, for higher temperatures, the capacitance drops, which provides excellent thermal self-regulating properties since in operation, the hottest capacitor will draw less current and vice versa, i.e. hotspots can be avoided, and the risk of a thermal runaway can be minimized.

Figure 9: DC bias dependence of ESR for different temperatures.\*

\* The 100% value corresponds to the typical ESR value as defined in the data sheet (i.e. typical ESR @ 0 V DC, 0.5 V AC, RMS, 1 kHz, room temperature)

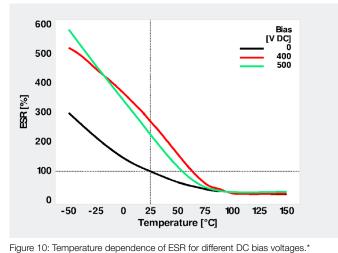

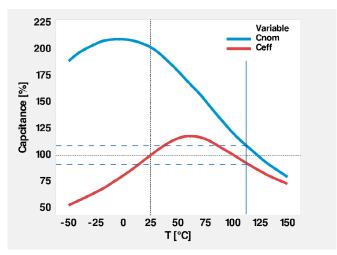

In Figure 11, the temperature dependence of the effective capacitance  $C_{\rm eff}$  and the nominal capacitance  $C_{\rm nom}$  is shown. As detailed previously,  $C_{\rm eff}$  and  $C_{\rm nom}$  corresponds to the small signal capacitance (small AC ripple) and the large signal capacitance (voltage signal spans full voltage range), evaluated at  $V_{\rm op}$  which in this

case is 400 V DC. Note that  $C_{nom}$  does not show the significant temperature drop in the low temperature regime as compared to  $C_{eff}$ . Above 70 °C operating temperature, dependence of the effective capacitance on AC ripple decreases and the two capacitances convergence.

The 100% value corresponds to  $C_{\text{eff, typ}}$  as defined in the data sheet (see <u>Table 1</u> in this document for an example).

Figure 11: Typical nominal capacitance C<sub>nom</sub> versus typical effective capacitance C<sub>eff</sub> for different temperatures for a LP 500 V.

## Capacitance

### Temperature dependence of capacitance

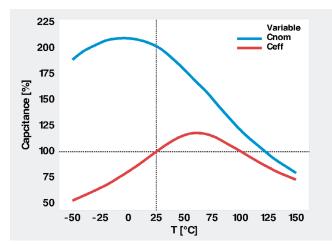

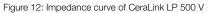

Furthermore, it is important to note that CeraLink is particularly designed for high switching frequencies, where at lower frequencies (below 10 kHz) ESR and impedance will be significantly higher as shown in Figure 12.

Optimal values are obtained in the range of 100 kHz to MHz at room temperature. However, as shown in Figure 10, the effective ESR for a realistic application temperature of 75 °C and higher, will be orders of magnitude lower.

As mentioned before, the dV/dt-ratio which can be applied, is limited only by the intrinsic ESR of the capacitor in principle. Same is true for short peak current pulses which are in principle limited only by two factors,

- 1. the overall induced voltage on the capacitor must stay below  $V_{{\mbox{\tiny pk,max}}}$  and

- 2. the induced device temperature stays within the rated limit.

V = 0 V DC, 0.5 V AC, RMS

## Capacitance

### Frequency dependence of capacitance

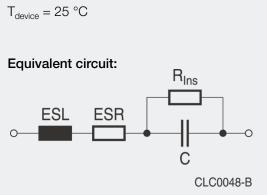

The frequency dependence of the small signal capacitance  $(C_0)$  is shown in Figure 13. Up to the resonance frequency at around 5 MHz, the capacitance is relatively constant.

Typical deviations of max. -3% in the frequency range 1 kHz to 1 MHz can be expected.

## Capacitance

### **Capacitance calculation**

In the following example we consider a CeraLink LP 500 V which has a typical effective capacitance  $C_{eff, typ} = 600 \text{ nF}$ . The application conditions are:

V DC <sub>bias</sub> = 350 V,  $f_{ripple}$  = 50 kHz,  $T_{device}$  = 115 °C.

Note that it is not relevant whether the device temperature is caused by the self-heating or by ambient temperature, i.e. it could be  $T_{amb} = 80$  °C and  $\Delta T = 35$  °C, resulting in  $T_{device} = 115$  °C.

Furthermore, we consider the three scenarios with

- ① a small, superimposed ripple voltage (0.5 V AC, RMS) – see green curve below

- an intermediate superimposed ripple voltage (20 V AC, RMS) – see red curve below

- ③ a large signal (voltage signal covers full voltage range) – see blue curve below

Figure 14: Small signal scenario (green), intermediate signal scenario (red) and large signal scenario (blue) for our calculation example.

## Capacitance

### **Capacitance calculation**

From the capacitance graphs in the CeraLink LP 500 V data sheet (see also Figure 15), the effective capacitance at a DC bias of 350 V DC and 25 °C is roughly 90%, i.e. 10% lower than at 400 V DC (see green curve). However, from the capacitance increase due to temperature, we obtain 114% for the 85 °C case (orange curve) and 95% for 125 °C case (red curve). By linear interpolation between these two values, we obtain for the 115 °C case roughly 109%, i.e. an increase of about +9% as compared to the  $C_{\rm eff}$ -value of 600 nF.

Figure 15: Capacitance values for these operating conditions.

We note that this calculational example should provide only an idea about the non-linear aspects of CeraLink capacitors. For a more detailed analysis of certain application conditions, we refer to our simulation tools on our website: <u>www.tdk-electronics.tdk.com.</u> As shown in Figure 13, the frequency dependence of the capacitance in this frequency region is approximately -2%. In total, the capacitance will change by about +7%. Therefore, the capacitance for the small signal scenario (1) for these operating conditions is about 640 nF. On the other hand, the capacitance for the intermediate signal scenario (2) for these application conditions will be around 700 nF, i.e. approximately 10% higher, whereas for scenario (3) we would have roughly 750 nF, i.e. 17% higher as shown in Figure 16.

Figure 16: Difference between  $\mathrm{C}_{\mathrm{eff}}$  and  $\mathrm{C}_{\mathrm{nom}}$  for these operating conditions.

## **Current capability**

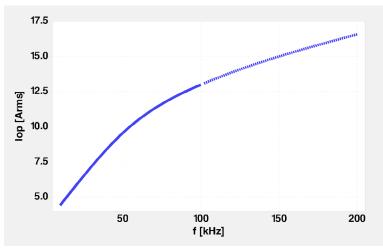

CeraLink is optimized for operation at high frequency and temperature. The ESR, shown in Figure 10, decreases significantly for higher frequencies or at high temperatures. Therefore, the efficiency and thus the current capability of the device gets better when operated in this regime.

This is also obvious from Figure 17 that shows the current capability of a CeraLink LP 500 V for different frequencies. Note that from 100 kHz to 200 kHz, the current capability can be increased by almost 30%.

$$T_{ambient} = 105 \ ^{\circ}C$$

$T_{device} = 150 \ ^{\circ}C$

Capacitor is mounted on an aluminum heatsink with forced airflow. Experimental setup is detailed in footnote on the following page

Figure 17: Current capability of a CeraLink LP 500 V for different frequencies.

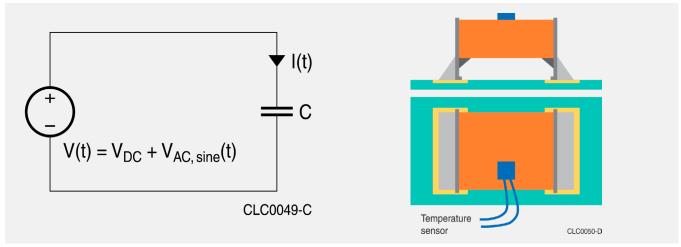

The current capability is measured using the setup shown in Figure 18.

Figure 18: Schematic circuit for the current capability measurements. The device temperature is measured using a standard PT100 probe that is glued directly on the ceramics.

Using a fixed DC-bias voltage of  $V_{op}$ , the superimposed sinusoidal ripple voltage amplitude  $V_{AC, sine}(t)$  is adjusted iteratively such that a current is established which leads to a fixed (pre-defined) device temperature (e.g. 150 °C). The temperature of the device is measured using a temperature sensor, which is attached to the top side of the ceramics.

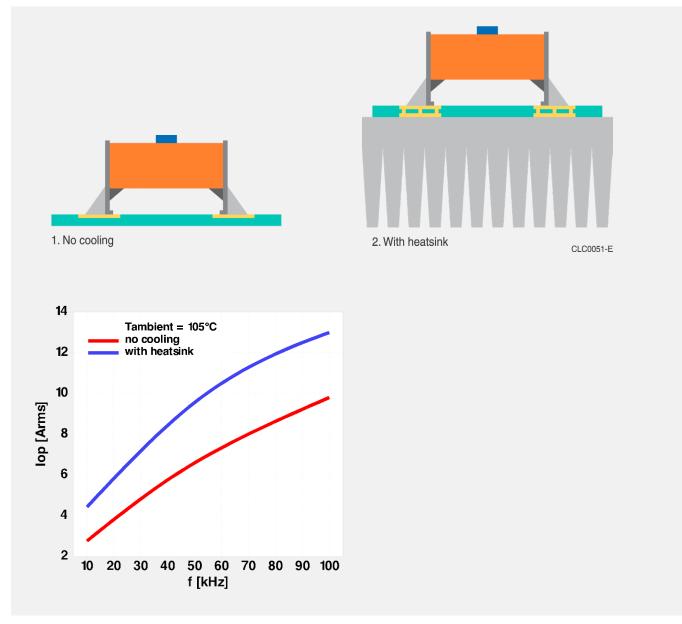

We note that the main heat transfer of CeraLink happens through thermal conduction through the copper inner electrodes and the termination (lead frames) to the PCB. Only a fraction of the heat is dissipated through convection to the air. Therefore, a good cooling concept, i.e. the efficient mounting to a heatsink, is of paramount importance to maximize the current capability of the device.

## **Current capability**

Figure 19 shows this concept schematically. In the first scenario, the device is only mounted on a PCB without any further cooling (no heatsink and no forced airflow). This is the usual setting for our data sheet measurements since it represents the worst-case condition. In the second

scenario, the device is mounted on the same PCB, however, this time with an additional aluminum heatsink and forced airflow\*. With additional cooling the current capability increases significantly, where the improvement at 10 kHz and 100 kHz is about 54% and 33%, respectively.

Figure 19: Current capability of CeraLink LP 500 V using two different cooling setups.

<sup>\*</sup> Throughout this experiment, a standard 40 mm x 75 mm x 100 mm aluminum heatsink was used which offers a thermal resistance of roughly 1.2-1.4 K/W, where for safety reasons the heatsink was isolated from the PCB by a layer of Kapton<sup>®</sup> foil. The forced airflow is provided by the oven fan. It is important to note, that this example should provide only an idea about the importance of a proper cooling concept, where the current capability in real application might be different since it depends on various factors such as thermal conductivity through PCB, electrical/thermal isolation, heatsink, housing etc.

## Polarization

In contrast to other ceramic capacitors, most CeraLink capacitors (except CeraLink 2220) are shipped with a defined polarity as marked on the case (see specification in data sheet). This chapter shall describe the reasons, why a polarity is defined and the proper usage for giving the user a feeling about what must be considered in application. Furthermore, we emphasize again, that an operation under constant polarity change (AC) is not recommended due to significantly higher losses.

Note that the polarity marking is mainly for incoming inspection purposes since the components are usually unpoled anyway after reflow soldering due to temperature effects. If operated at normal DC-Link conditions, i.e. at voltage levels  $\geq V_{op}$ , the poling happens automatically

during the first seconds after switching on the DC-Link voltage. However, if the components are operated below the specified operational voltage  $V_{op}$ , a first-time poling is required to establish the full capacitance. The corresponding procedure and further background information shall be detailed in the following.

Because of its specific material features, CeraLink can be in poled, unpoled or reversely poled state or have a status somewhere in between. The polarity of CeraLink can be removed or changed in the opposite direction by application of voltage and/or temperature over time. So basically, there are three methods to change or remove polarity of CeraLink: voltage, time and temperature.

### Voltage

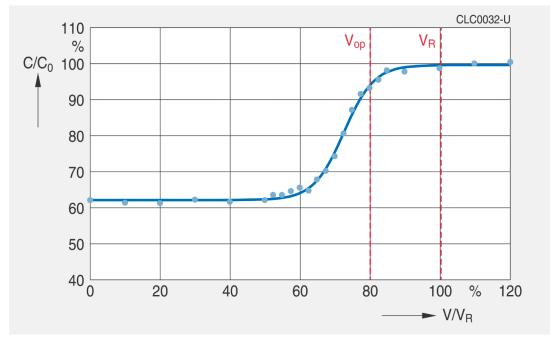

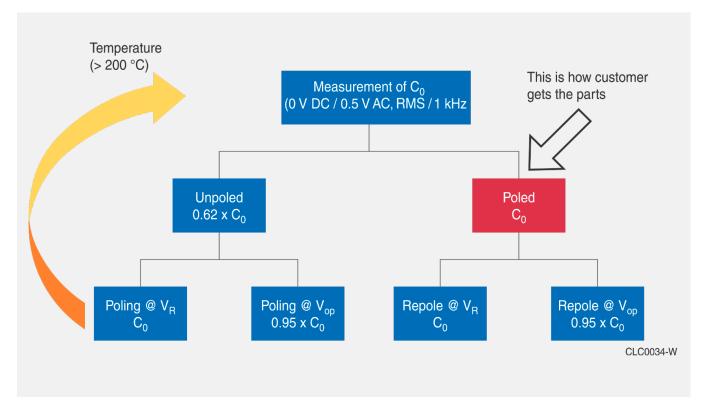

Applying voltage causes poling of CeraLink in the applied voltage direction. If enough voltage is applied, the polarization state is fully developed. Note that an unpoled CeraLink has only around 60% of its initial capacitance. As shown in Figure 20, the required voltage V to fully pole CeraLink is in the range of 90% to 95% of the rated

voltage V<sub>R</sub>. Note that with operating voltage V<sub>op</sub> the full polarity is usually not established (since V<sub>op</sub> < V<sub>R</sub>). This is particularly true for the 500 V types for which V<sub>op</sub> is 400 V, i.e. only 80% of the rated voltage, where for the 700 V and 900 V types the ratio is 86% and 89% respectively.

Figure 20: Required voltage to re-pole a CeraLink capacitor.

## Polarization

### Voltage

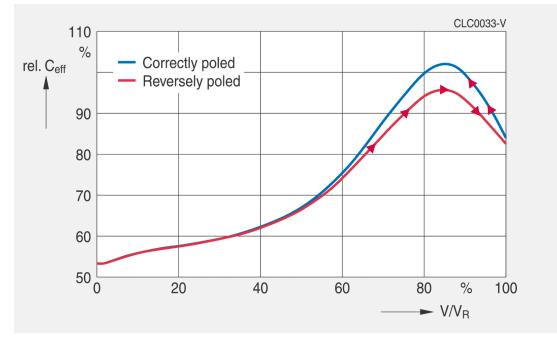

It is important to note, that the polarity can be fully reversed in the opposite direction, when sufficient negative bias is applied. In this case, the poling state changes independent of time, it only must be ensured that the full negative voltage is applied to the capacitor. The measured capacitance in poling and in reverse poling direction is shown in Figure 21. Note that the difference in capacitance will be only visible at around operating voltage. For small electrical fields, there is no difference in capacitance, whereas at voltage levels close to rated voltage, the device gets basically poled during the measurement and the two curves have roughly the same endpoint. When going back to 0 V, the originally "correctly poled" curve is reached again (in reverse direction).

Figure 21: Measured capacitance in poling and in reverse poling direction.

### **De-polarization over time**

CeraLink partly loses polarity over time if no voltage is applied. Typical decay rates at room temperature are approximately 2.5% per decade. That means when capacitance is measured for example one hour after poling, the capacitance after 10 hours will be 97.5% of the initial value, after 100 hours it will be 95%.

#### **De-polarization over temperature**

The unpoling effect mentioned above can be accelerated if the device is exposed to temperature. In practical terms, this happens during reflow soldering. Application of typical reflow solder profiles with peak temperatures of approximately 240 to 260 °C and an overall duration in the range of several minutes will lead to partial unpoling of the CeraLink capacitor. Both effects (loosing polarity by time and/or temperature) can be totally recovered by applying rated voltage  $V_{\rm R}$  (see section Voltage).

## Polarization

## Overview

Measuring the small signal capacitance  $C_0$  only allows one to determine the difference between the poled and unpoled states. Since there is no given direction in the measurement, the direction of polarity cannot be

determined. By applying rated voltage, the part under test poles itself automatically to the given direction. In Figure 22, the previously mentioned properties are highlighted schematically:

Figure 22: Schematic description of the relation between poling state and capacitance value for CeraLink

## Lifetime model & lifetime estimation

The lifetime of CeraLink depends on the applied voltage level and the device temperature in the application. The lifetime acceleration parameters are determined by a Highly Accelerated Life Test (HALT). From a comparison of the Weibull-distributed end-of-life measurements at different voltage levels and temperatures, the lifetime at a specific operating condition can be assessed from an Arrhenius law of the following formula:

$$t_{char,app} = t_{char,ref} \left(\frac{U_{ref}}{U_{app}}\right)^n \times \exp\left[\frac{E_a}{k_b} \left(\frac{1}{T_{app}} - \frac{1}{T_{ref}}\right)\right]$$

k<sub>b</sub> ... Boltzmann constant (8,617 333 262 x 10<sup>-5</sup> eV/K)

| Model inputs             | Parameters            |                                                               | 500 V Type                       | 700 V Type                       | 900 V Type                        |

|--------------------------|-----------------------|---------------------------------------------------------------|----------------------------------|----------------------------------|-----------------------------------|

| Model                    | n                     | voltage exponent 3.8                                          |                                  |                                  |                                   |

| parameters               | Ea                    | activation energy (in eV)                                     | activation energy (in eV) 1.2    |                                  |                                   |

| D.(                      | U <sub>ref</sub>      | reference voltage level (in Volt)                             | 600 V<br>(150% V <sub>op</sub> ) | 900 V<br>(150% V <sub>op</sub> ) | 1200 V<br>(150% V <sub>op</sub> ) |

| Reference<br>conditions* | T <sub>ref</sub>      | reference temperature (in Kelvin)                             | 473.15K (200 °C)                 |                                  | )                                 |

|                          | t <sub>char,ref</sub> | characteristic lifetime under reference conditions (in hours) | 580 hours                        |                                  |                                   |

| Application              | U <sub>app</sub>      | device voltage level in application (in Volt)                 | - User input                     |                                  |                                   |

| conditions               | T <sub>app</sub>      | device temperature in application (in Kelvin)                 |                                  |                                  |                                   |

\* Note that the stated reference conditions might be different to our in-house testing conditions. The stated reference characteristic lifetime is valid for reference condition 200 °C and 150% V<sub>op</sub>. Conversion between different conditions can be done via above Arrhenius formula. The model parameters (e.g. the activation energy) are based on experimental data and might be updated periodically.

| Model output | Parameters            |                                                                 |

|--------------|-----------------------|-----------------------------------------------------------------|

|              | t <sub>char,app</sub> | characteristic lifetime under application conditions (in hours) |

### Characteristic lifetime, reliability and failure distribution

From the Arrhenius law stated above, the characteristic lifetime  $t_{char,app}$  is obtained for a given device voltage  $U_{app}$  and the device temperature  $T_{app}$  in the application.

Once the characteristic lifetime is obtained, the corresponding reliability function is given by a Weibull distribution of the formula:

$$R(t) = exp\left[-\left(\frac{t}{\tau_{char,app}}\right)^{\beta}\right]$$

R(t) describes the probability that the component is still "alive" at time *t*. The parameter  $\beta$  denotes the steepness of the Weibull distribution and is obtained from HALT

measurements. For CeraLink, this parameter is typically fixed to  $\beta = 2.5$ .

## CeraLink lifetime model & lifetime estimation

Characteristic lifetime, reliability and failure distribution

Note that since  $\beta \neq 1$  the failure rate  $\lambda$ , which is related to the derivative of R(t), obtains the more general formula:

$$\lambda(t) \equiv -\frac{1}{R(t)} \frac{dR(t)}{dt} = \frac{\beta}{\tau_{char,app}} \left(\frac{t}{\tau_{char,app}}\right)^{\beta-1}$$

Hence the failure rate has a time dependence, i.e. depends on the operating time t of the system. This makes it less useful for a practical lifetime assessment

such that it is often more convenient to consider the cumulative failure distribution function F(t) defined by:

$$F(t) \equiv 1 - R(t)$$

F(t) describes the cumulative failure amount, i.e. the probability that the component has failed at a certain time *t*. By inverting this function, the specific lifetime *t*

for a given pre-defined cumulative failure amount (e.g. 0.1% or 100 ppm) can be determined using:

$$(F) = \tau_{char,app} \times ln \left(\frac{1}{1-F}\right)^{\beta^{-1}}$$

t

Note that also the often-used mean time to failure (MTTF) must be written in the more general formula:

$$MTTF = \tau_{char,app} \times \Gamma\left[1 + \frac{1}{\beta}\right]$$

Where the gamma function reduces to  $\Gamma[2]=1$  for  $\beta =1$ .

How to use these formulas is exemplified in the following Calculation Example I.

### Systems of identical chips

The generalization to a system of multiple identical chips is straightforward. Let us consider the following series system of N identical components:

In this configuration the entire system fails if any of the individual components fail (a parallelization of ceramic capacitors is, in fact, a series system, since if one of the individual capacitors goes short the whole capacitor module or array goes short). The resulting reliability function of this system of N identical components is given by:

$$R_{system}(t) = \prod_{i=1}^{N} exp\left[-\left(\frac{t}{\tau_{app,char}}\right)^{\beta}\right] = exp\left[-N\left(\frac{t}{\tau_{app,char}}\right)^{\beta}\right] = exp\left[-\left(\frac{t}{\tilde{\tau}_{app,char}}\right)^{\beta}\right]$$

## CeraLink lifetime model & lifetime estimation

Systems of identical chips

To bring the equation to equal form, we introduced the re-scaled characteristic lifetime:

$$\tilde{\tau}_{app,char} \equiv \frac{\tau_{app,char}}{\sqrt[\beta]{N}}$$

Similar as in the previous case, the failure rate and MTTF is given by:

$$MTTF_{system} = \tilde{\tau}_{char,app} \times \Gamma \left[ 1 + \frac{1}{\beta} \right]$$

### Mission profiles and combined failure distributions

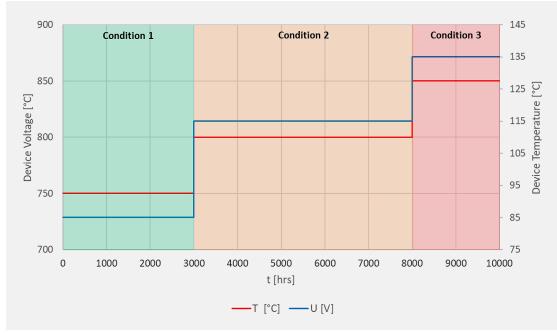

In a realistic application, the conditions (device temperature and applied voltage) are usually not constant but vary significantly throughout the lifetime of the device. To some extent this complex behavior can be approximated by a mission profile which groups the continuous up and down of temperature and voltage into several subsequent constant regions (see Figure 23 for an example). The generalization of the previous approach when considering several subsequent application conditions is straightforward. The resulting reliability function is the product of the individual reliability functions and thus given by:

$$R_{total}(t_1; \dots; t_N) = \prod_{i=1}^{N} R_i(t_i) = \prod_{i=1}^{N} exp \left[ -\left(\frac{t_i}{\tau_{app,char}^{(i)}}\right)^{\beta} \right]$$

With the individual characteristic lifetimes  $\tau_{app,char}^{(i)}$  and operating times  $t_i$  the system is operated under a specific application condition "i" (i.e. a specific device temperature and voltage).

Analogously, the cumulative failure distribution function is defined by:

$$F_{total}(t_1; ...; t_N) \equiv 1 - R_{total}(t_1; ...; t_N)$$

This generalized approach is exemplified in the following Calculation Example II – Simplified Mission Profile.

Finally, when considering the mission profile approach for a system of identical chips the total reliability function is given by:

$$R_{total}(t_1; ...; t_N) = \prod_{i=1}^{N} exp\left[-M\left(\frac{t_i}{\tau_{app,char}^{(i)}}\right)^{\beta}\right] = \prod_{i=1}^{N} exp\left[-\left(\frac{t_i}{\tilde{\tau}_{app,char}^{(i)}}\right)^{\beta}\right]$$

Where analogously to the previous section we introduced the re-scaled characteristic lifetime:

$$\tilde{\tau}_{app,char}^{(i)} \equiv \frac{\tau_{app,char}^{(i)}}{\frac{\beta}{\sqrt{M}}}, \quad \text{with } i \in [1, \dots, N]$$

And "M" is the number of identical chips.

## CeraLink lifetime model & lifetime estimation

Calculation example I – constant operating conditions

In this example we consider the CeraLink LP 500 V type. Throughout, three different operating temperatures and two different voltage levels are examined.

Note that for the lifetime calculation, the operating temperature and voltage experienced by the chip is important. For the operating temperature it is irrelevant whether the chip is heated up due to electrical current flow or through the ambient temperature. Table 2 shows the characteristic lifetime in hours as well as the lifetime for 1% and 10 ppm failure amount and the MTTF. Note that due to the underlying Weibull–type distribution, 63.2% of the samples will have statistically failed after the characteristic lifetime.

It is important to note that this example calculation provides only a rough assessment. For a more detailed estimation of the lifetime, a dedicated mission profile is required (see also next example).

| U <sub>op</sub> T <sub>op</sub> | 100 °C                               | 125 °C                               | 150 °C                    |

|---------------------------------|--------------------------------------|--------------------------------------|---------------------------|

|                                 | $	au_{char,app} = 7.21 \times 10^6$  | $\tau_{char,app} = 6.92 \times 10^5$ | $\tau_{char,app} = 87700$ |

| 400 M                           | $MTTF = 6.40 \times 10^6$            | $MTTF = 6.14 \times 10^5$            | $MTTF = 7.78 \times 10^4$ |

| 400 V                           | $t_{1\%} = 1.15 	imes 10^6$          | $t_{1\%} = 1.10 \times 10^5$         | $t_{1\%} = 13900$         |

|                                 | $t_{10ppm} = 72100$                  | $t_{10ppm} = 6920$                   | $t_{10ppm} = 877$         |

|                                 | $\tau_{char,app} = 3.09 \times 10^6$ | $\tau_{char,app} = 2.97 \times 10^5$ | $\tau_{char,app} = 37600$ |

| 500 V                           | $MTTF = 2.74 \times 10^6$            | $MTTF = 2.63 \times 10^5$            | $MTTF = 3.33 \times 10^4$ |

|                                 | $t_{1\%} = 4.90 \times 10^5$         | $t_{1\%} = 47100$                    | $t_{1\%} = 5960$          |

|                                 | $t_{10ppm} = 30900$                  | $t_{10ppm} = 2970$                   | $t_{10ppm} = 376$         |

Table 2: Lifetime calculation CeraLink LP 500 V. All shown lifetimes in hours.

TDK points out that the experimental test boundary condition for no failure is the High Temperature Operational Life test (MIL-STD-202, method 108) at rated voltage and 150 °C for 1000 hours. Nevertheless, due to the statistical nature of the failure mechanism, a zero-failure rate within this time cannot be guaranteed.

## CeraLink lifetime model & lifetime estimation

### Calculation example II – simplified mission profile

We consider the following mission profile for a CeraLink LP 900 V type, with three discrete operating conditions:

750 V DC/85 °C, 800 V DC/115 °C and 850 V DC/135 °C

Figure 23: Simple mission profile.

The contributions of the individual conditions are given by:

**Condition 1:** Characteristic lifetime:  $\tau_1 = 4.42 \times 10^7$  hrs The cumulative failure amount is given by (using  $t_1 = 3000$  hrs):

$$F_1(t_1) = 1 - exp\left[-\left(\frac{t_1}{\tau_1}\right)^{\beta}\right] = 3.80 \times 10^{-11} = 0.038 \, ppb$$

**Condition 2:** Characteristic lifetime:  $\tau_2 = 1.71 \times 10^6$  hrs The cumulative failure amount is given by (using  $t_2 = 5000$  hrs):

$$F_2(t_2) = 1 - exp\left[-\left(\frac{t_2}{\tau_2}\right)^{\beta}\right] = 4.62 \times 10^{-7} = 0.462 \ ppm$$

**Condition 3:** Characteristic lifetime:  $\tau_3 = 2.34 \times 10^5$  hrs The cumulative failure amount is given by (using  $t_3 = 2000$  hrs):

$$F_3(t_3) = 1 - exp\left[-\left(\frac{t_3}{\tau_3}\right)^{\beta}\right] = 6.67 \times 10^{-6} = 6.67 \, ppm$$

The combined contributions, i.e. the total cumulative failure amount after 10 k hours is given by:

$$F_{total}(t_1; t_2; t_3) = 1 - exp\left[-\left(\frac{t_1}{\tau_1}\right)^{\beta}\right] exp\left[-\left(\frac{t_2}{\tau_2}\right)^{\beta}\right] exp\left[-\left(\frac{t_3}{\tau_3}\right)^{\beta}\right] = 7.22 \times 10^{-6} = 7.22 \ ppm$$

### Frequently asked questions

### How do I detect if CeraLink is poled or unpoled?

Measure the small signal capacitance  $C_0$  as described in the data sheet (usually done at 0 VDC, 0.5 VAC, RMS, 1 kHz). If  $C_0$  is only approximately 60% of the data sheet value, CeraLink is unpoled (note that this is the usual case after reflow soldering).

### CeraLink seems to be partly poled/unpoled (e.g. after reflow soldering). How shall I proceed?

During operation, i.e. when DC bias voltage  $\geq V_{op}$  is applied, CeraLink gets poled. If you want to make sure to have a fully poled component before operation, apply rated voltage V<sub>R</sub> to the component. This is of particular importance in cases when the capacitor is not operated constantly, e.g. in protection circuits. In this case, the application of a defined voltage profile after reflow soldering is recommended to ensure a fully poled device in case of failure (voltage pre-conditioning).

### If CeraLink is poled, how do I detect the poling direction?

The only possible way to detect the direction of polarity of a CeraLink is by measuring the effective capacitance  $C_{eff}$ , i.e. performing the  $C_0$  measurement with DC bias (note that  $C_{eff}$  is defined as  $C_0$  at operating voltage  $V_{op}$ ). In this case, a slightly smaller capacitance value would be

measured on a reversely poled CeraLink, see Figure 20. This effect is most prominent for the 500 V type and less distinctive for the higher voltage classes (see previous statement). In general, the easier solution is to reset the polarity by applying rated voltage  $V_{\rm B}$ .

### What happens if a CeraLink capacitor is mounted in the wrong polarity direction?

- a) If V<sub>R</sub> is applied, the capacitor is re-poled during first switching on and no further action is needed.

- b) If V<sub>op</sub> is applied in application, two scenarios should be considered:

- V<sub>op</sub> with a small superimposed ripple voltage (small signal): the capacitor will be poled to a level of ≥ 95%, i.e. there will be a capacitance loss of ≤ 5%.

- V<sub>op</sub> with a large superimposed ripple voltage (large signal): the additional ripple amplitude is usually enough to fully pole CeraLink.

- c) If <V<sub>op</sub> is applied in application, mounting CeraLink capacitor in pre-defined polarity is recommended. Note that after reflow soldering and/or time exposure, CeraLink is partly unpoled (see chapter <u>>Polarization<</u>).

#### Figure 24: Polarity marking of CeraLink LP.

Description on polarity marking is mentioned in the respective data sheet after dimensional drawing and solder pad recommendation. As an example, Figure 24 shows polarity marking of CeraLink LP version. Note that polarity is only for incoming inspection purposes, and it does not affect operation. If put under reverse rated voltage  $V_{\rm R}$ , CeraLink is repoled and works identically. Note furthermore, that CeraLink 2220 components do not have polarity marking at all (due to the aforementioned reasons).

### **Frequently asked questions**

You mention there is no limitation on dv/dt. How is this to be understood in regard to voltage or current peaks in the milliseconds range?

The dV/dt ratio is limited only by the intrinsic ESR of the capacitor, where the time constant is given by  $\tau = ESR \cdot C$ . It is difficult to give a general value for  $\tau$  since the ESR of CeraLink is a non-linear quantity and depends on frequency and temperature. However, for typical application conditions, the time constant will be in the nanoseconds range, i.e. well below the microseconds range.

Furthermore, we note that there is no limit on di/dt in principle, i.e. short peak current pulses are basically limited only by two factors 1) the overall induced voltage (e.g. from stray inductance or large inductive loads) on the capacitor must stay below  $V_{pk, max}$  and 2) the induced device temperature stays within the rated limits.

### What do I have to consider in regard to conformal coating?

Depending on the expected contamination of the P.C. board in application a conformal coating might be necessary to meet normative requirements on creepage distance (in case of doubt regarding potential chemical intolerances please contact TDK). In general, we don't recommend potting or encapsulation of CeraLink with stiff epoxy-based materials since this will potentially introduce cracks in the ceramics. Soft, gel-type potting materials which are typically used in power module integration are better suited. In any case, please consult TDK when potting or encapsulation is considered for a particular application.

### What do I have to consider in regard to creepage and clearance distance?

CeraLink ceramic typically has a relatively large Comparative Tracking Index (CTI) of ≥600, and therefore fulfills the requirements on creepage and clearance distance according to IEC 60664-1 for degree of contamination 1 or 2 for all voltage types:

| Degree of contamination |               |               |                 |

|-------------------------|---------------|---------------|-----------------|

| CeraLink V classes      | 1             | 2             | 3               |

| 500 V (LP & FA)         | (>1.3 mm) Yes | (>2.5 mm) Yes | Not recommended |

| 700 V (LP & FA)         | (>2.0 mm) Yes | (>3.5 mm) Yes | Not recommended |

| 900 V (LP & FA)         | (>3.2 mm) Yes | (>4.5 mm) Yes | Not recommended |

Table 3: Creepage distance requirements according to IEC 60664-1 Table F.5 for contamination class 1 & 2 are fulfilled for all CeraLink LP & FA types.

| Degree of contamination |               |               |                 |

|-------------------------|---------------|---------------|-----------------|

| CeraLink V classes      | 1             | 2             | 3               |

| 500 V (2220)            | (>1.3 mm) Yes | (>2.5 mm) Yes | Not recommended |

| 900 V (2220)            | (>3.2 mm) Yes | (>4.5 mm) No  | Not recommended |

Table 4: Note that the creepage distance requirement according to IEC 60664-1 Table F.5 for contamination class 2 is not fulfilled for the CeraLink 2220 900 V. Additional measures (e.g. conformal coating and/or slitting of PCB) are recommended for this type.

## Frequently asked questions

Which soldering processes are applicable for CeraLink?

| CeraLink series | Reflow *    | Wave            | Other (e.g. Vapor phase) |

|-----------------|-------------|-----------------|--------------------------|

| LP, FA          | Recommended | Not recommended | Please consult TDK       |

| SP (terminated) | Recommended | Recommended     | Please consult TDK       |

| 2220            | Recommended | Not recommended | Please consult TDK       |

Table 5: Soldering processes

#### How can I repair/rework soldering on CeraLink?

Manual soldering with a soldering iron must be avoided. If not otherwise possible hot-air methods are recommended for repair purposes.

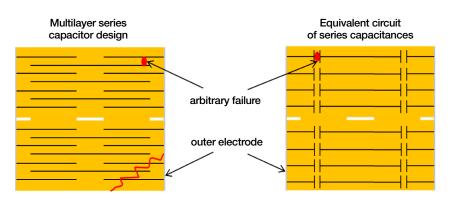

### Is CeraLink using the classical MLCC design?

The CeraLink ceramic chip features a multilayer serial connection (MLSC) design, i.e. a series connection of two MLCC geometries in one component as shown in Figure 25. This design offers additional safety as compared to standard MLCC design and can reduce the risk of short circuits caused by ceramic cracks (e.g. resulting from mechanical overstress) since if one side of the MLSC is short, the other side can theoretically withstand rated voltage  $V_R$  (with a reduction of overall lifetime). Furthermore, the risk of surface arcing or other surface migration effects (e.g. Ag migration) is minimized using MLSC.

Nevertheless, the MLSC design should be considered only as a safety feature and cannot prevent short-circuit. This is particularly true for high power/voltage applications in which a short-circuit on one side of the MLSC can affect the other side as well due to the large energy stored. Hence, as a matter of principle, a ceramic crack in a CeraLink or overvoltage can lead to a shortcircuit, like other ceramic capacitors. Furthermore, the capacitance density of MLSC is decreased as compared to MLCC design.

Note that CeraLink 2220 series is designed for highest capacitance density and therefore features the classical MLCC design. In this case, the risk of ceramic cracking is reduced via an additional soft termination layer (for soft termination type only).

Figure 25: MLSC design of CeraLink standard chip (LP, FA & SP).

\* Reflow soldering profiles according to IEC 60068-2-58 recommendations. For details, please check the respective product data sheet. The usage of lead-free solder types is recommended.

### Frequently asked questions

### Why can CeraLink handle so much current?

CeraLink chips feature copper inner electrodes, which provide not only excellent electrical conductance and low losses but also outstanding thermal properties, i.e. the heat produced inside the chip is transported to the outer contacts (leadframes) and subsequently to the PCB very efficiently.

The connection between CeraLink ceramic body and outer contacts is a sintered layer of silver, where the outer contacts are made of CIC (copper-invar-copper), which combines highest electrical and thermal conductivity with low coefficient of thermal expansion (CTE). Furthermore, the CTE is matched to the ceramic such that thermo-mechanical stress of the whole system is minimized.

In conclusion, all employed materials provide excellent thermal and electrical conductivity (lowest thermal and electrical resistance) allowing to transfer the component heat efficiently through the lead frames to the PCB. This is especially the case for CeraLink LP and FA series. However, it is important to have a good cooling concept for the current handling as shown in chapter <u>>Current</u> <u>Capability</u>. Note that all data sheet values are based upon worst-case scenarios (mounting on standard FR4, no heatsink, no active airflow).

## Pulse current and inrush current?

The pulse current capability of CeraLink is typically several orders of magnitude larger than the continuous (RMS) current capability which is specified in the data sheet. Pulse currents may even go up to several kA without harming the device. However, it strongly depends on the application conditions if such a current pulse will induce a harmful voltage on the device (e.g. due to the overall inductance in the system).

Furthermore, very large current pulses may induce heat spots within the capacitor leading to localized defects in the ceramic material. On the other hand, a pulse which is not critical as a singular event may heat up the capacitor significantly if applied subsequently. In this case the pulse currents need to be considered as they contribute to the self-heating. Hence the pulse current capability is typically not stated in the data sheet and needs to be tested for the individual application. Please consult TDK in case of questions regarding pulse current capability of CeraLink for a particular application.

Inrush current is a parameter more related and discussed for other capacitor technologies such as e.g. "Metalized polypropylene film capacitors" or "alu capacitors". In the case of ceramic capacitors, there is usually not such a restriction.

### How much lead (pb) contains CeraLink?

CeraLink ceramic contains roughly 60 wt% of lead (Pb) in a covalent/ionic bond.

Note that for CeraLink the <u>RoHS exemption 7(c)-II</u>, Lead in dielectric ceramic in capacitors for a rated voltage of 125 V AC or 250 V DC or higher; is valid. Thus, CeraLink capacitors can be used without any further restriction. Further details on this topic as well as on the material composition are available in the material data sheet on our website: <u>www.tdk-electronics.tdk.com</u>

## Frequently asked questions

### Which MSL does apply?

In general, CeraLink components are not moisture sensitive and therefore the Moisture Sensitivity Level (MSL) does not apply. If required, MSL = 1 can be used. Nevertheless, use CeraLink as soon as possible after opening factory seals such as polyvinyl-sealed packages since the solderability might degrade (particularly, when exposed to corrosive atmosphere).

### Are balancing resistors needed when connecting CeraLink in series?

Voltage imbalances can lead to an asymmetrical operation of capacitors in a serial connection in which one of the capacitors will operate at lower voltage while the other one operates at higher voltage (compared to the symmetric case). Here, a slight voltage imbalance is usually not critical. However, in some cases it might be necessary to implement balancing resistors to compensate for this imbalance. The voltage imbalance might be introduced by different device temperatures between the capacitors leading to slightly different capacitance and ESR values. However, we note that even though CeraLink shows a non-linear behavior over temperature and voltage, the temperature differences are usually not sufficient to lead to a significant imbalance. Also, the CeraLink ceramics features some self-regulating properties such that is quite unlikely that the two capacitors in series will drift apart. Nevertheless, please consult TDK in case of doubt.

| A | <b>/</b> pt | bei | nd | ice | s |

|---|-------------|-----|----|-----|---|

|   |             |     |    |     |   |

| Glossary                                  |                                                                                                                                               |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Symbols                                   | Terms                                                                                                                                         |

| AC                                        | Alternating current                                                                                                                           |

| C <sub>0</sub>                            | Initial capacitance @ 0 V DC, 0.5 V AC, RMS, 1 kHz, room temperature                                                                          |

| C <sub>eff</sub> (C <sub>eff, typ</sub> ) | Typical effective capacitance @ V <sub>op</sub> , 0.5 V AC, RMS, 1 kHz, room temperature                                                      |

| C <sub>nom</sub> (C <sub>nom, typ</sub> ) | Typical nominal capacitance @ V <sub>op</sub> , quasistatic, room temperature                                                                 |

| CTE                                       | Coefficient of thermal expansion                                                                                                              |

| CTI                                       | Comparative tracking index                                                                                                                    |

| DC                                        | Direct current                                                                                                                                |

| ESL                                       | Equivalent serial inductance                                                                                                                  |

| ESR                                       | Equivalent serial resistance                                                                                                                  |

| FA                                        | Flex assembly                                                                                                                                 |

| f <sub>ripple</sub>                       | Frequency of the operation ripple current                                                                                                     |

| I <sub>op</sub>                           | Operating ripple current, root mean square value of sinusoidal AC current                                                                     |

| LP                                        | Low profile                                                                                                                                   |

| MLCC                                      | Multilayer ceramic capacitor                                                                                                                  |

| MLSC                                      | Multilayer serial capacitor                                                                                                                   |

| PCB                                       | Printed circuit board                                                                                                                         |

| PLZT                                      | Lead lanthanum zirconium titanate                                                                                                             |

| ppm                                       | Parts per million                                                                                                                             |

| R <sub>ins</sub>                          | Insulation resistance @ $V_{pk}$ , measurement time t = 7 s, room temperature                                                                 |

| SP                                        | Solder pin (note that this component is terminated with 04/2024)                                                                              |

| T <sub>amb</sub>                          | Ambient temperature                                                                                                                           |

| tan δ                                     | Dissipation factor @ 0 V DC, 0.5 V AC, RMS, 1 kHz, room temperature                                                                           |

| T <sub>device</sub>                       | Device temperature. $T_{\rm device}$ = $T_{\rm amb}$ + $\Delta T$ ( $\Delta T$ defines the self-heating of the device due to applied current) |

| V <sub>op</sub>                           | Operating voltage                                                                                                                             |

| V <sub>R</sub>                            | Rated voltage                                                                                                                                 |

| V <sub>AC, RMS</sub>                      | Root mean square value of sinusoidal AC voltage                                                                                               |

| V <sub>pk, max</sub>                      | Maximum peak operating voltage                                                                                                                |

| ΔΤ                                        | Increase of temperature during operation                                                                                                      |

## Appendices

### CeraLink data sheet

Please find all our latest CeraLink data sheet on the TDK webpage here: <u>Product catalog: CeraLink capacitors | TDK Electronics - TDK Europe</u> <u>CeraLink Capacitors | Products | TDK Product Center</u>

### **Design support**

TDK is continuously working on extending its library of design support tools. On TDK webpages several possible use cases/functions are shown in application notes.

### **Contact information**

For further information and support, please contact our team via the following email address: <a href="mailto:ceralink@tdk.com">ceralink@tdk.com</a>

| Revision history |                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------|

| Revision         | Changes                                                                                                |

| V2 (July 2024)   | Marking of CeraLink SP series as terminated, update of lifetime estimation, new FAQ, editorial changes |

| V1 (Jan 2021)    | Original                                                                                               |

Important information: Some parts of this publication contain statements about the suitability of our products for certain areas of application. These statements are based on our knowledge of typical requirements that are often placed on our products. We expressly point out that these statements cannot be regarded as binding statements about the suitability of our products for a particular customer application. It is incumbent on the customer to check and decide whether a product is suitable for use in a particular application. This publication is only a brief product survey which may be changed from time to time. Our products are described in detail in our data sheets. The Important notes (www.tdk-electronics.tdk.com/ImportantNotes) and the product-specific Cautions and warnings must be observed. All relevant information is available through our sales offices.

© TDK Electronics AG Edition 08/2024 www.tdk-electronics.tdk.com